计算机组成原理

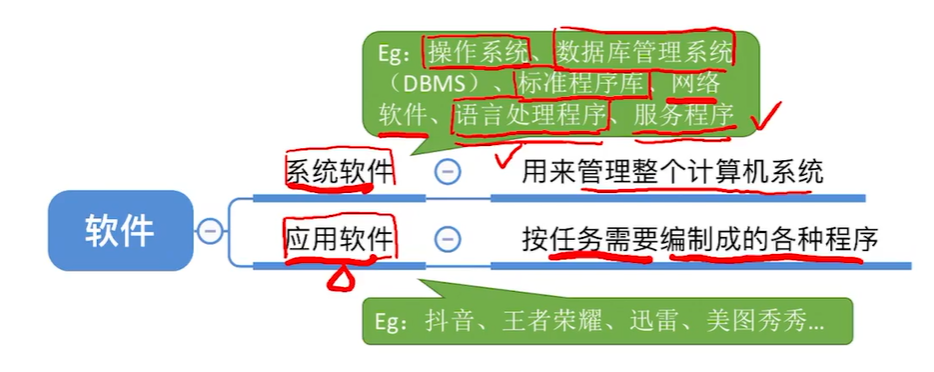

软件

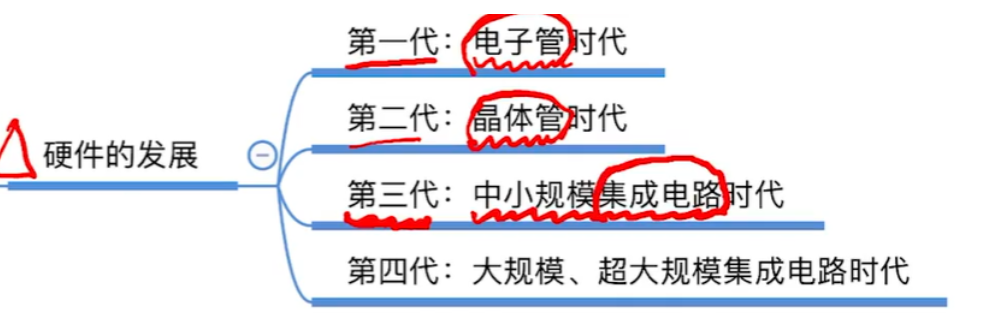

硬件

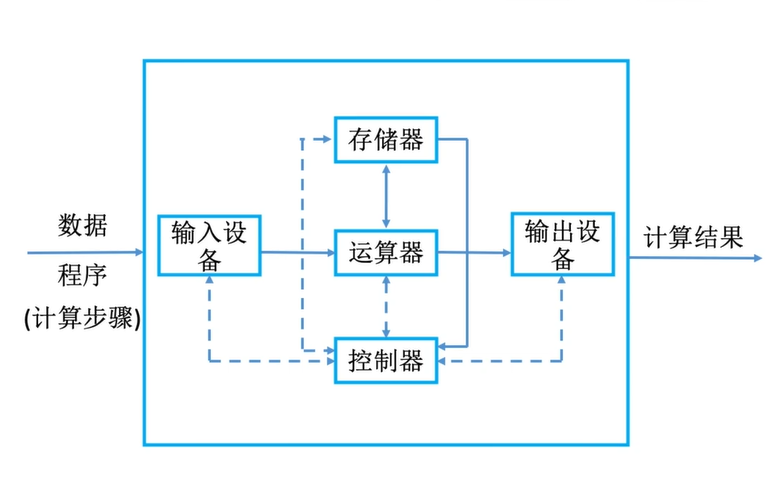

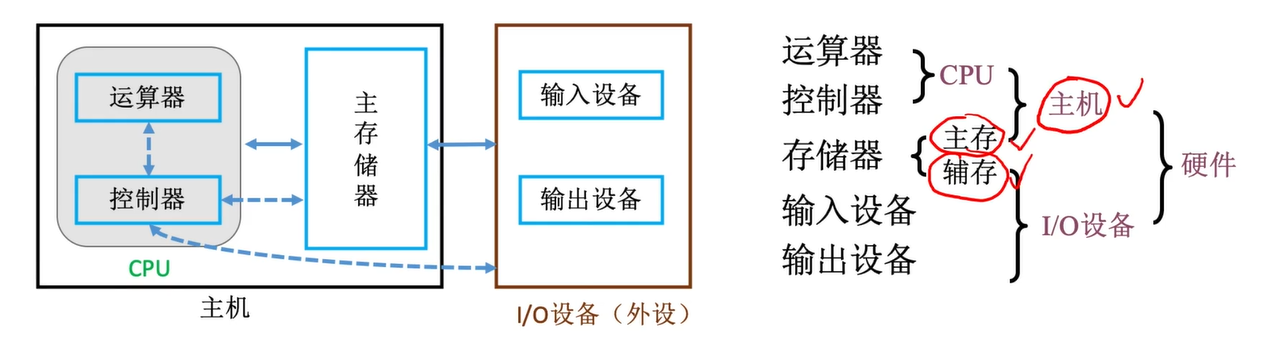

1.冯诺依曼

ENIAC手动接线代表指令。冯诺依曼将指令存储起来

运算器为中心,数据要经过运算器。

现代的将存储器为中心

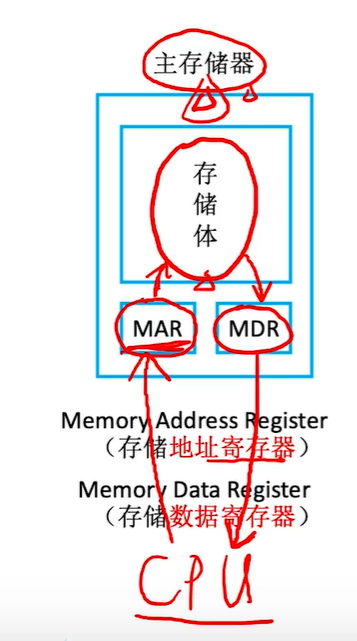

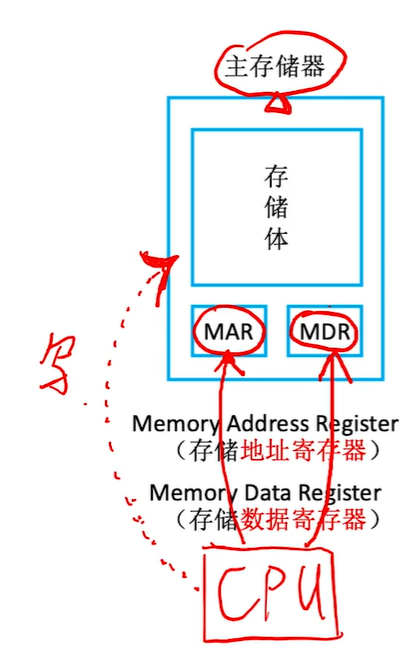

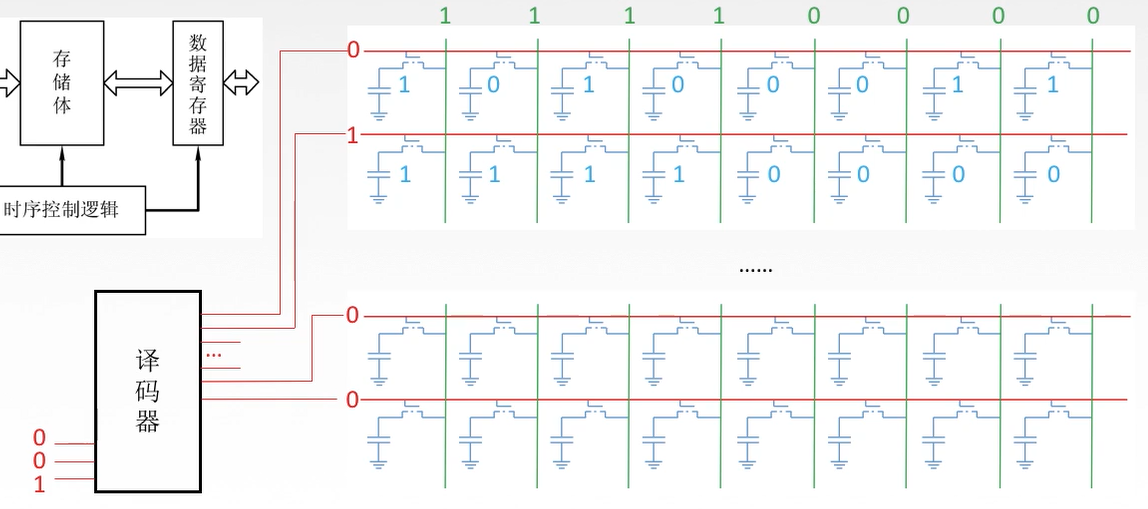

主存储器

取存数据的程,现代这两个寄存器继承到了cpu里面

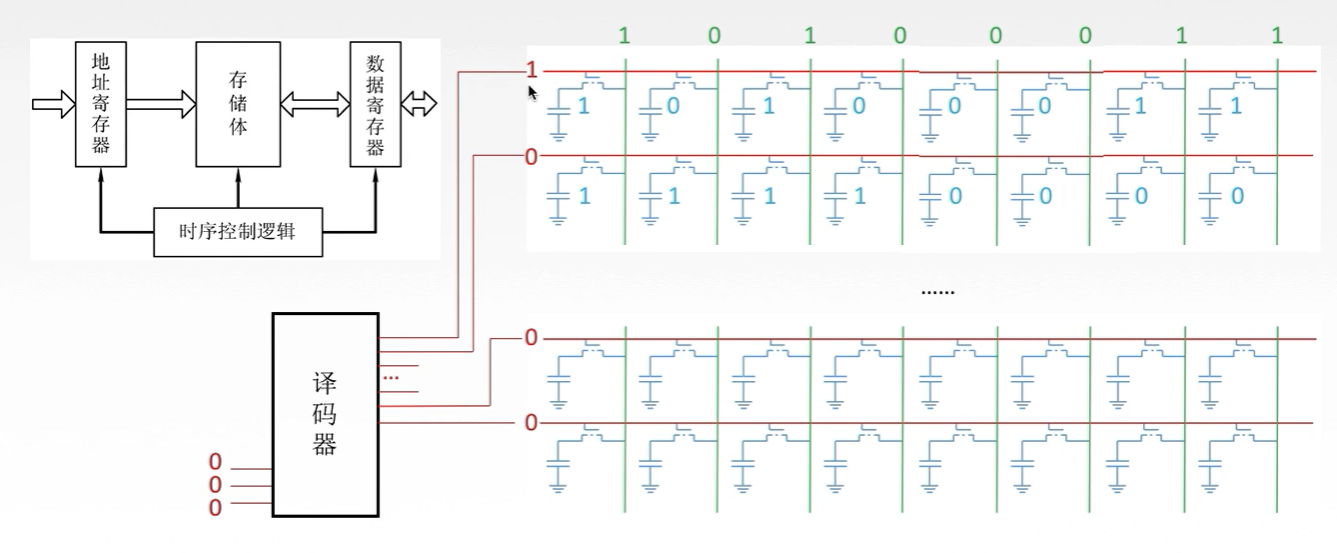

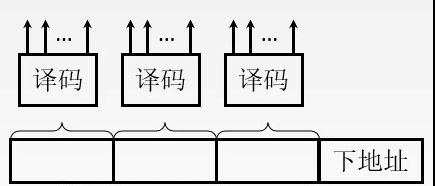

通过译码器将地址转为one hot,1的那个为接通

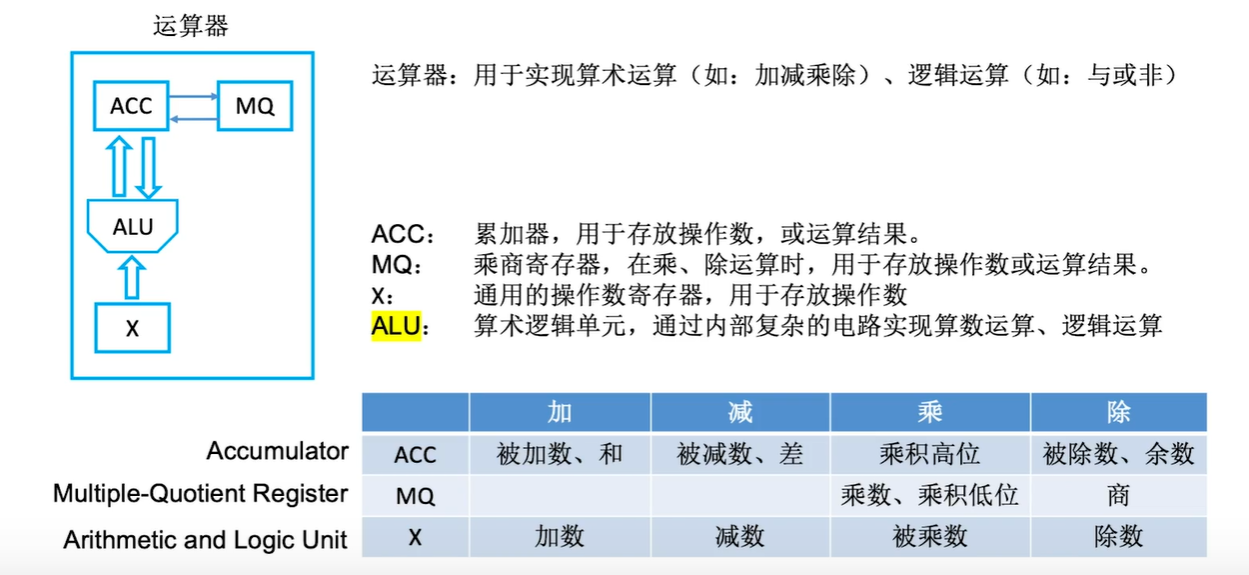

运算器

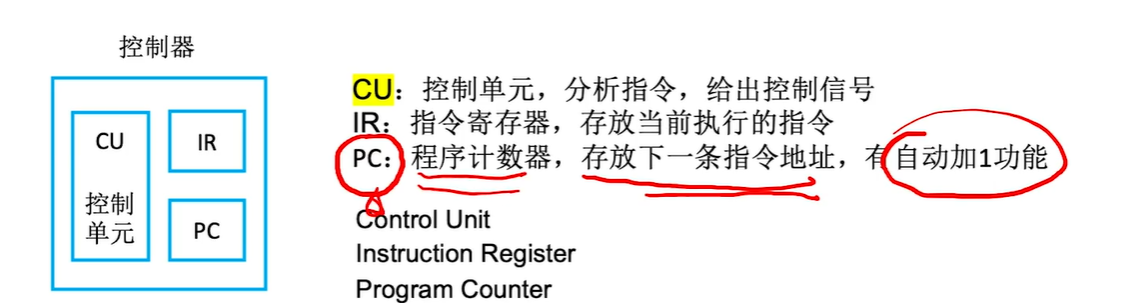

控制器

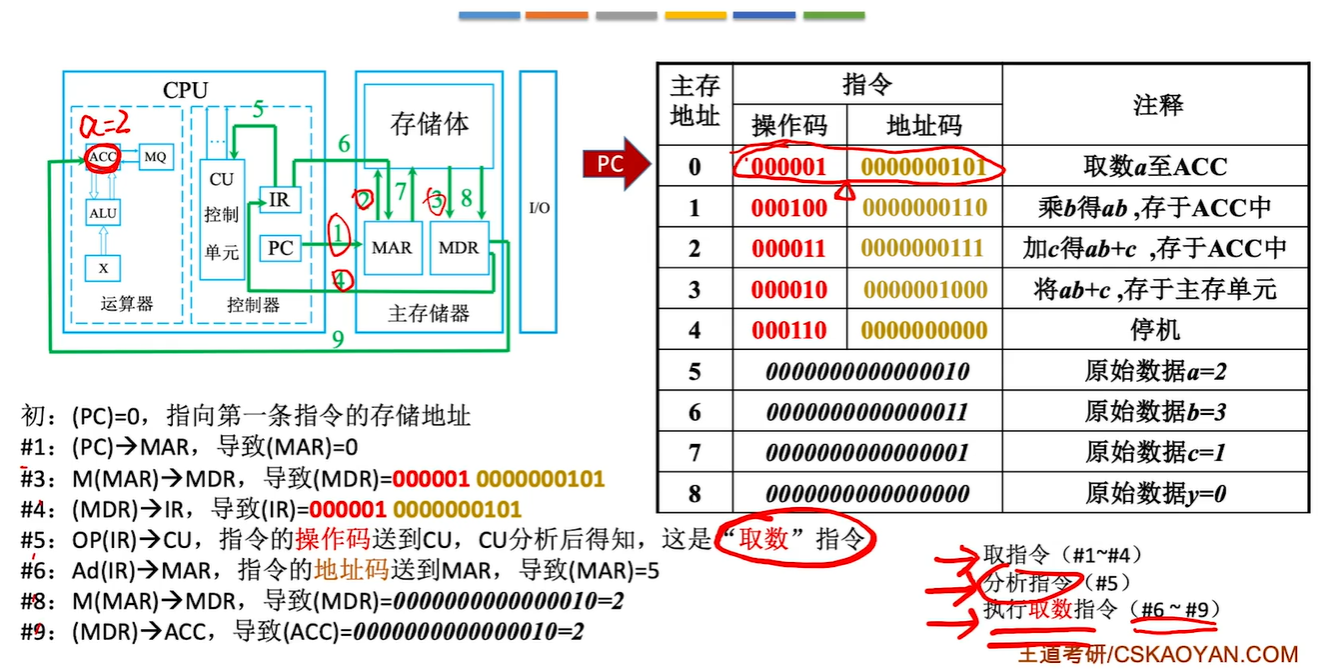

举例

a * b + c 的执行过程,高级语言转为指令存放到内存中。这里的指令是单地址指令

根据pc从内存取指令(初始0) -> 分析指令(操作码) -> 执行指令内容 指令和数据都是来自存储体

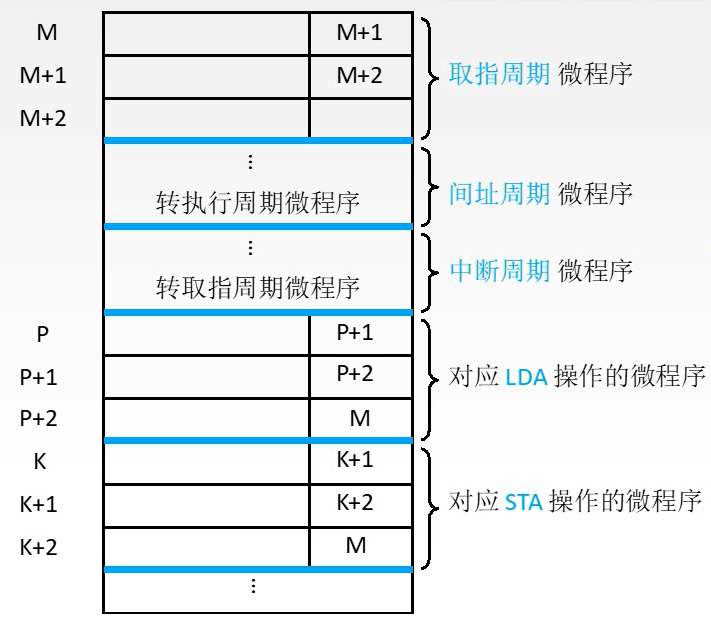

将机器指令转换为多条微指令

高级语言 ->(编译) 汇编语言 -> 操作系统 ->(汇编) 机器语言 01 -> 微指令

或者直接将高级语言转为机器语言(python)逐句翻译

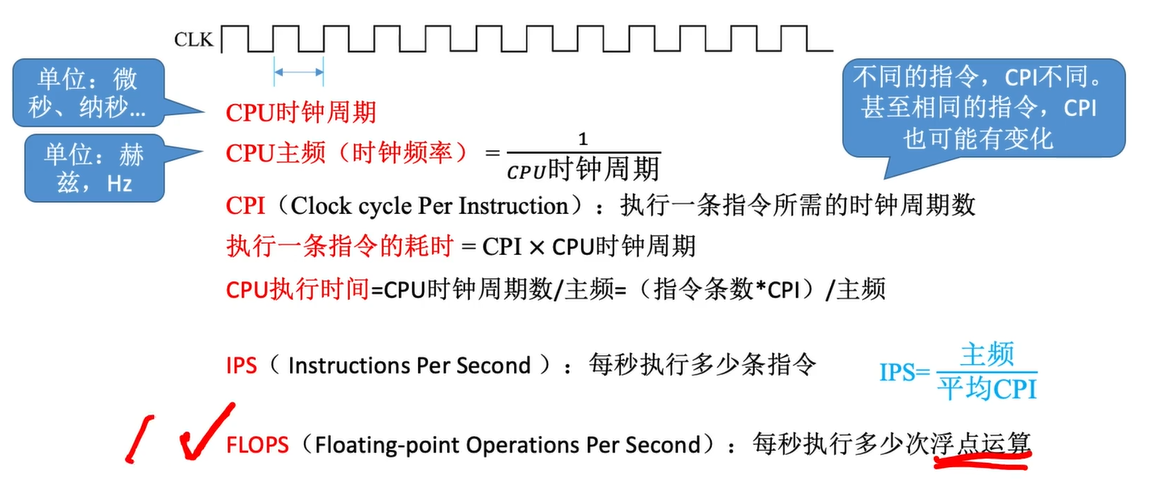

主频

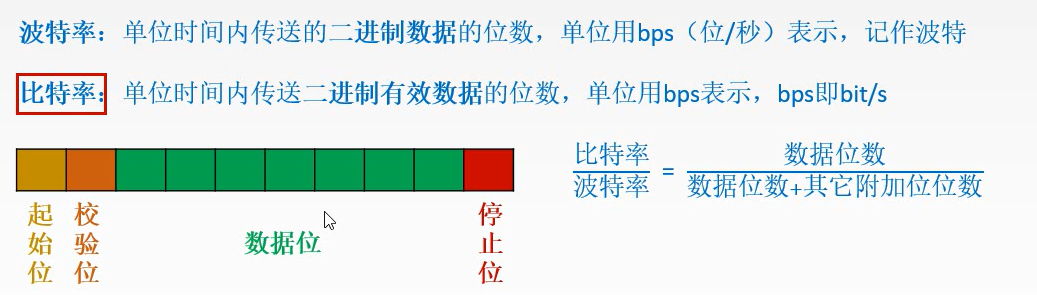

波特率比特率

2.基础

1.进制转换

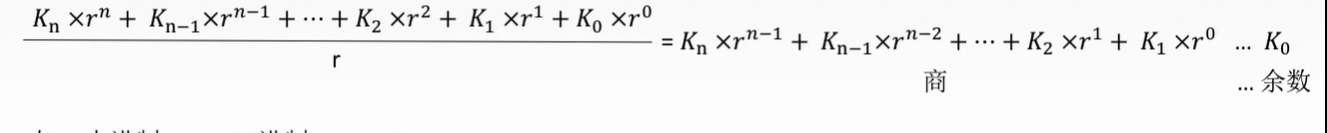

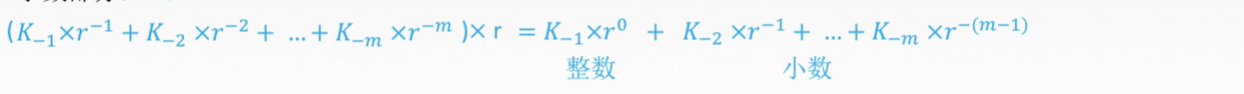

十进制转其他

整数除基取余

小数乘基取整

二进制转其他(4、8、16):多位一组,分组转换

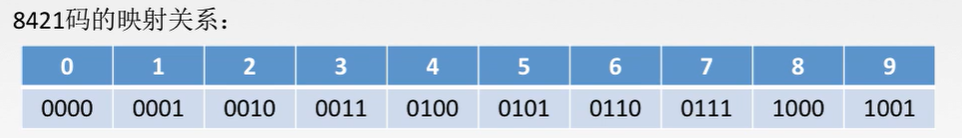

2.BCD码

用二进制表达十进制数,当超过10时需要加6修正

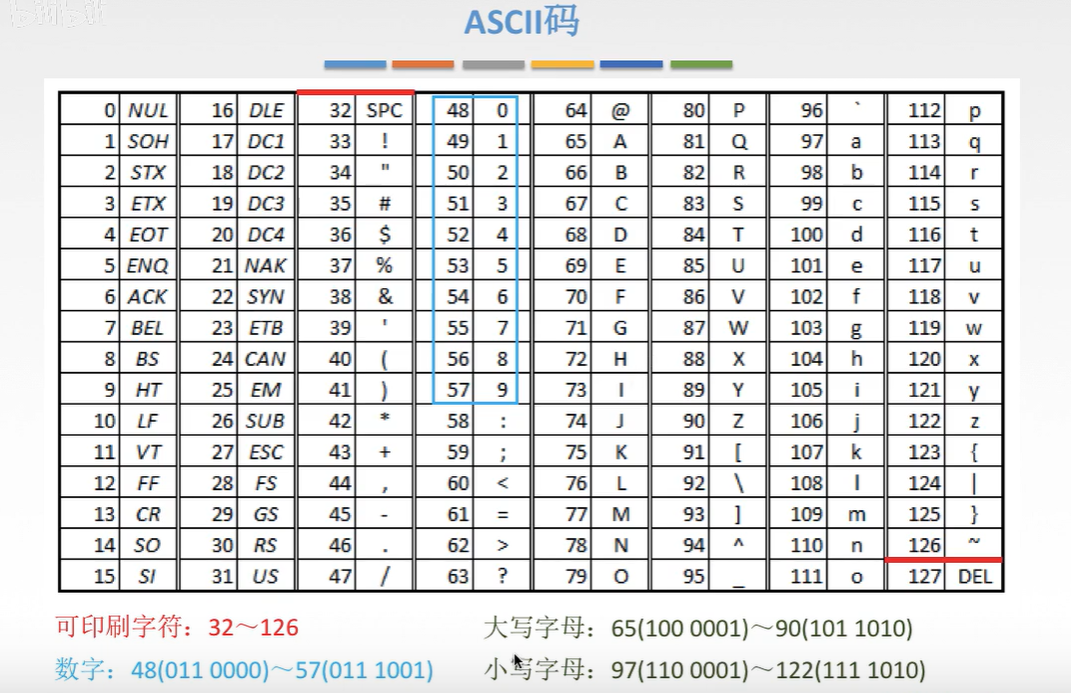

3.ASCII

汉字7445个,需要2B

4.校验

奇校验:加完校验1的个数为奇数个,一般放前面

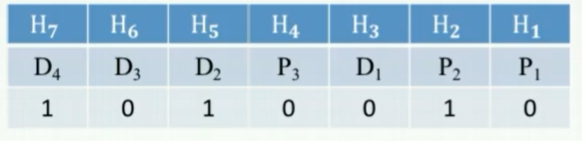

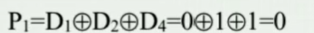

海明校验:p的位置为2^n,标记出出错位置

d为数据,p为校验码

pi为d为1的下标上第i为异或得到,共需要大约log2位用来校验

循环冗余校验CRC :

有一个给出的生成多项式,最高为x次 ,转为二进制被除数1101有x+1位,将数据左移x位后除以该数(模二除),得到的余数就是校验位。发送 移位后的数 加上 余数。

,转为二进制被除数1101有x+1位,将数据左移x位后除以该数(模二除),得到的余数就是校验位。发送 移位后的数 加上 余数。

校验:数据模二除多项式,余数为零

5.数据表示

无符号数: 0 ~ 2^n-1

有符号数:一位表示符号

定点小数:纯小数。0. x,再加一位表示符号

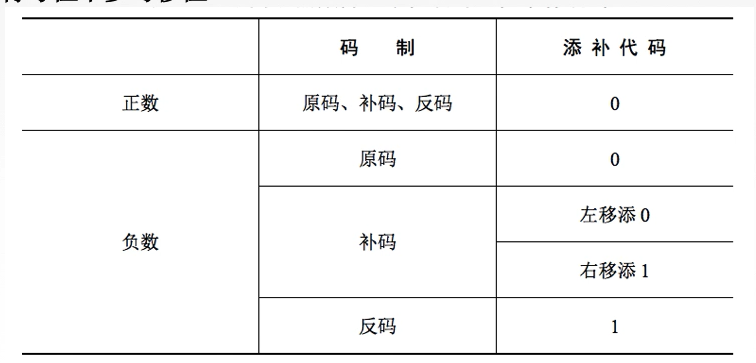

原码:有符号数 ,加减计算需要讨论符号

,加减计算需要讨论符号

反码:负数按位取反

补码:负数按位取反,末尾加一(原理上是用溢出值减绝对值)。计算直接加

移码:加上128后,转为无符号机器数。比较大小

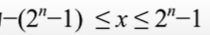

移位:

溢出判断

1.通过符号判断

2.进位判断法:V= S异或C 其中S为符号位产生的进位,C为最高有效位产生的进位。

3.双符号位: V=Sf1 Sf2 + 其中,Sf1和Sf2分别为最高符号位及第二符号位。

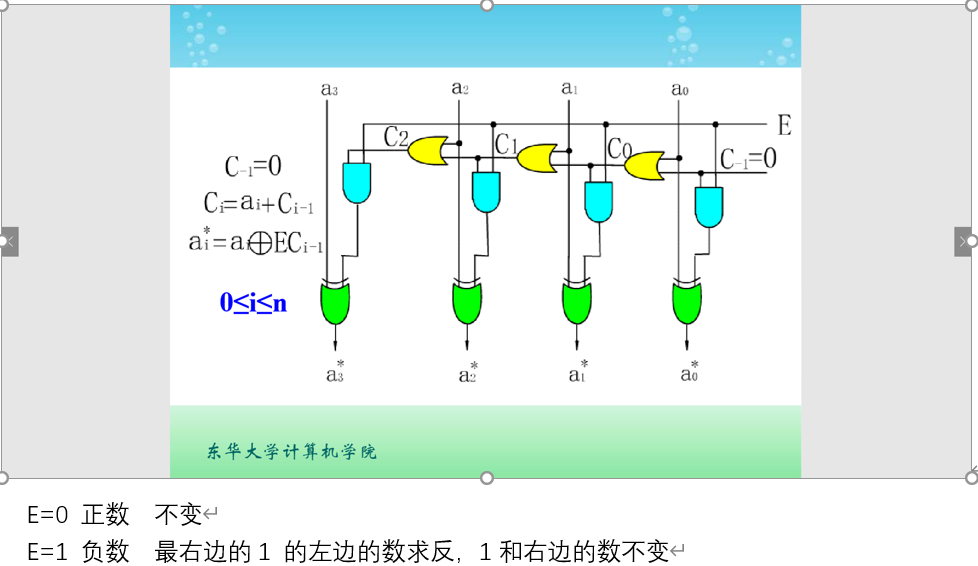

求补电路:

将补码表示的带符号数转换成 无符号绝对值

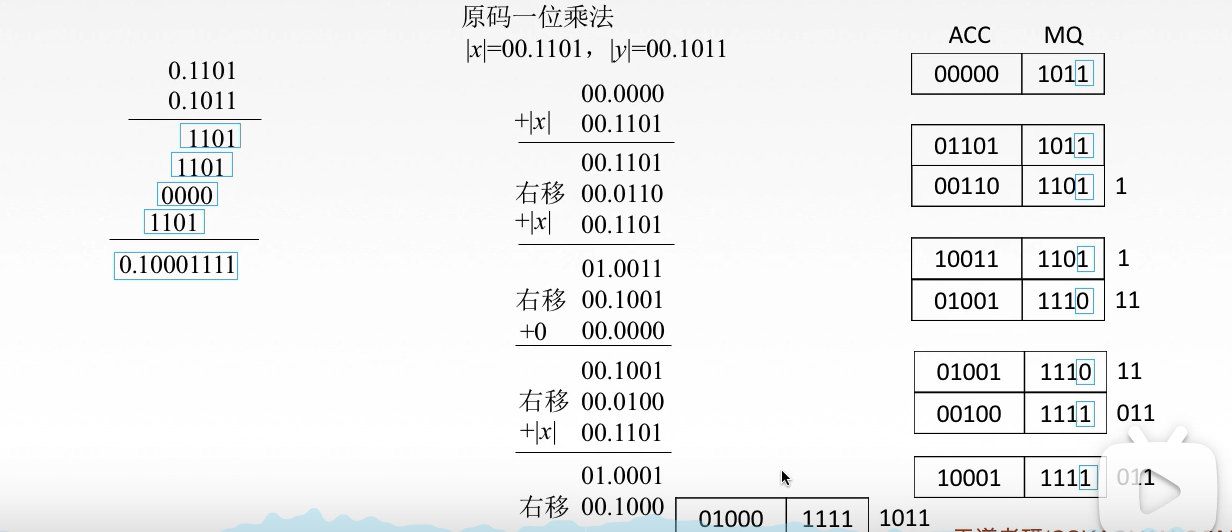

绝对值乘法

acc中保存当前进位,MQ高位保存结果以及低位未计算的乘数,当乘数都移出去后,结果就是ACC MQ

绝对值除法

ACC中放当前值,MQ中放结果

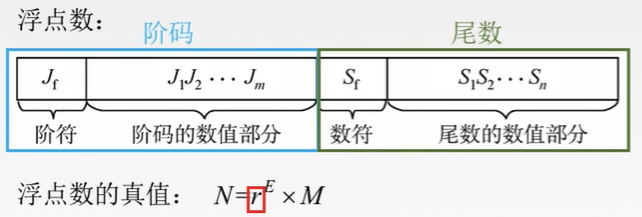

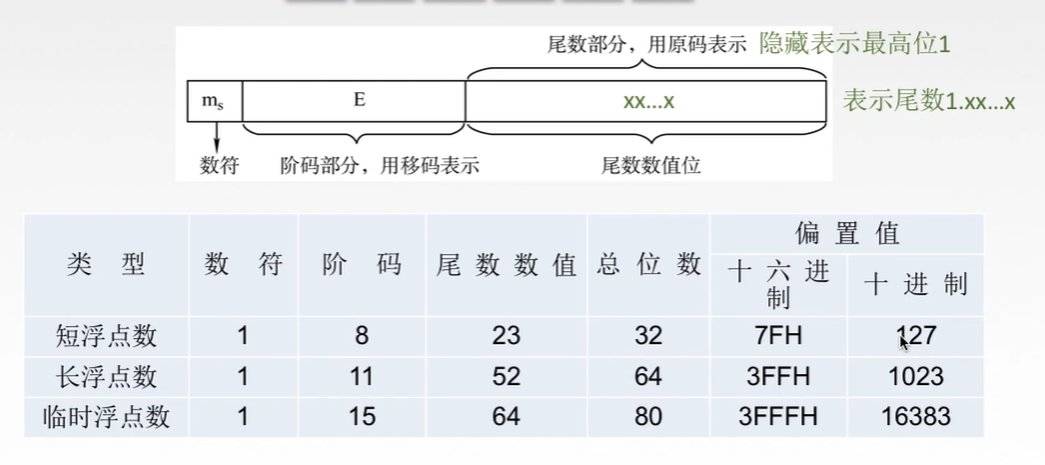

浮点数表示

规格化,M左移使得最高位有效

溢出时,将M右移

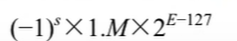

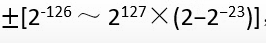

IEEE 754

)

)

浮点数运算:小阶向大阶看齐

ALU

Arithmetic and logic unit 算数、逻辑、移位

与非: 现实容易实现

现实容易实现

异或: 和加法的逻辑类似

和加法的逻辑类似

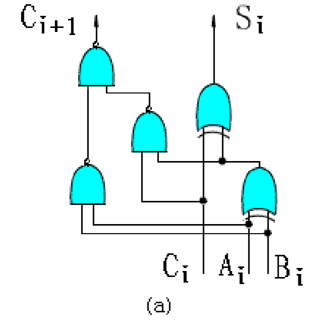

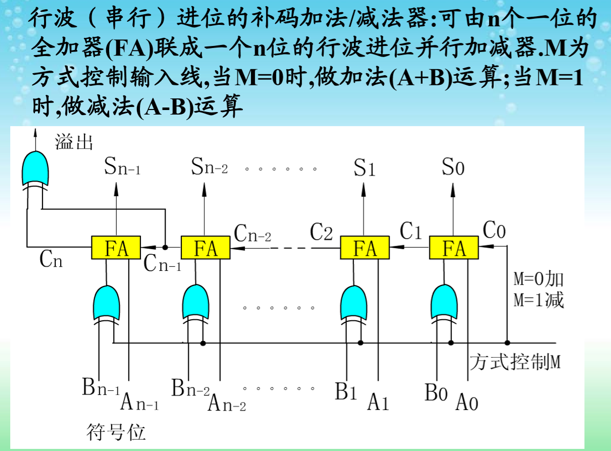

全加器:

多位串行:

并行

组内并行,组间串行

3.存储器

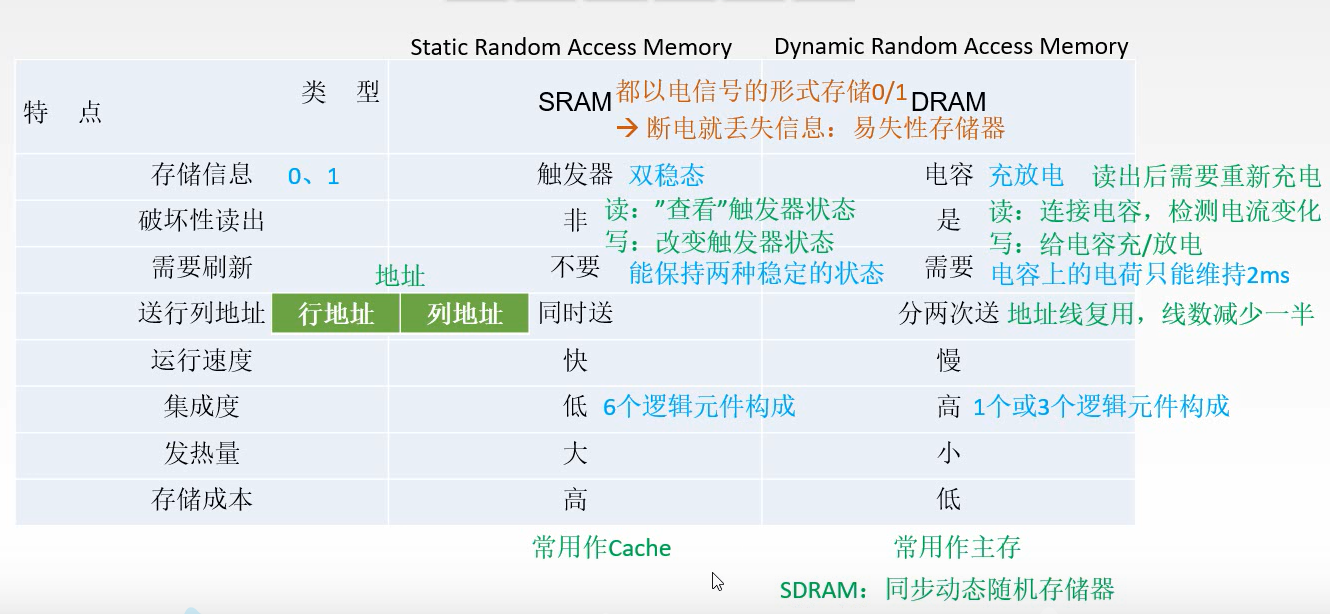

读取过程:地址线先传送地址数据到MAR,略微等待后片选线和读写控制线给出信号,将数据读入MDR中

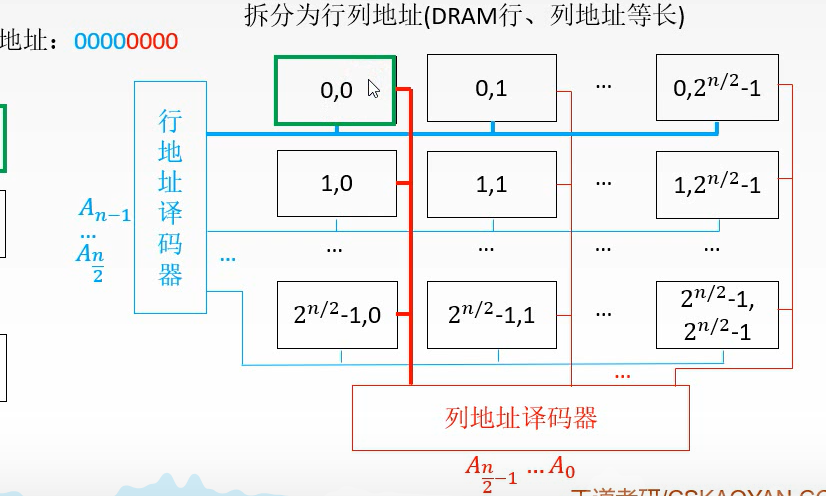

实际上,地址是有行选和列选(需要的线少一倍),刷新时是以行为单位。

地址线连接MAR(行列分别传入),数据线连接MDR

寻址方式:按字、字节、半字、双字寻址

存储方法:

小段方式:先放低位字节,低位在左

大段方式:先放高位,高位在左

半导体存储器

辅存不和cpu直接通信,主存RAM+ROM

RAM

Random Access Memory

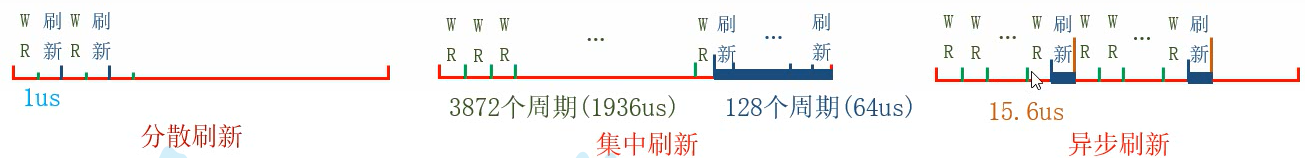

刷新时间:2ms要都刷新过一次。

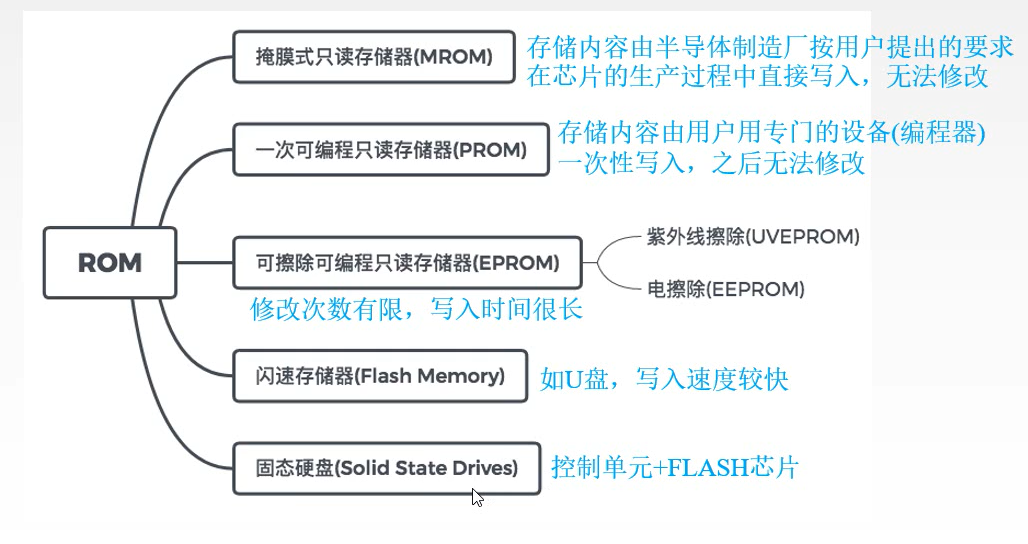

ROM

Read only Memory

保存必要信息,非易失。保存os在辅存中的位置,开机必要信息

扩展

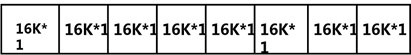

位扩展:

进行位数的扩充(加大字长) 一个存储器对应byte中的一位

例:使用16K1的存储器芯片组成16K8位的存储器

字扩展法:

进行字向扩充(位数不变) 需要先选择取哪个存储器

例如:用16K*8位的芯片组成64K *8位的存储器

A0~A13为地址选择 A14 A15为芯片选择(2:4译码器)

字位同时扩展法:

一个存储器的容量为MN位,若使用 lk位的芯片(l<M,K<N),需要在字向和位向同时进行扩展. 此时共需(M/l)*(N/k)个存储器芯片

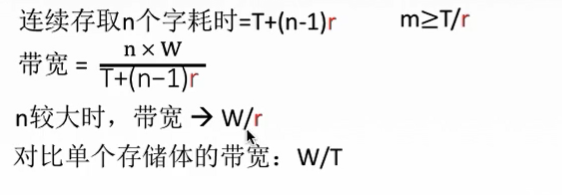

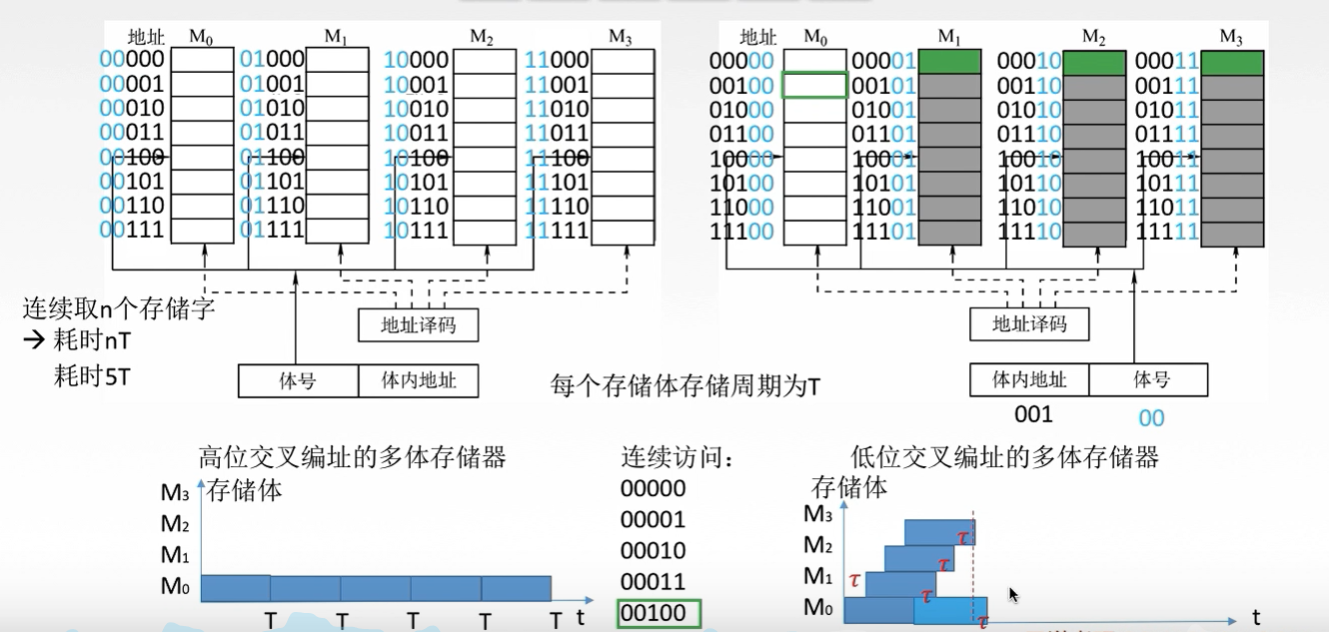

多体并行存储体

低位交叉编址

(右图)将相邻的单元放到不同的存储体中,这样不需要等待恢复时间再去读取下一个(流水线)

需要满足当再一次读取到M0时,M0已经恢复

宏观上扩展了4倍

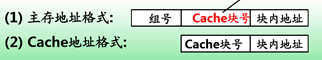

cache

空间局部性原理(访问的都是相近的元素)

cache和主存可以以块为单位交流

标记项:cache是从主存中哪里来的、cache是否有效

全相联映射

随便放,查找时遍历查看

直接映射:

主存第j块和Cache第i块有如下函数关系:

i= j mod m (m为Cache中总块数)

访问过程:依据cache块号直接去查找,看表中对应保存的组号与主存中组号是否一样。

空间利用率低,命中率也低,硬件实现简单,成本低.

组相联映射:

将cache分组,主存必须放入对应组中,但组内可以随意放置

替换与修改

RAND FIFO LRU(最近最少使用) LFU(历史次数)

写回法:脏位决定是否需要写回

全写法:有一个缓冲同时修改

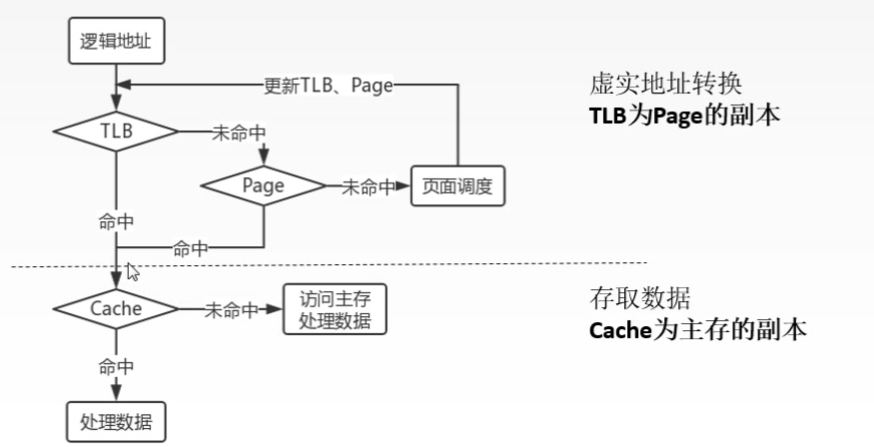

虚拟存储

将访问外存(逻辑地址)映射到主存(物理地址)

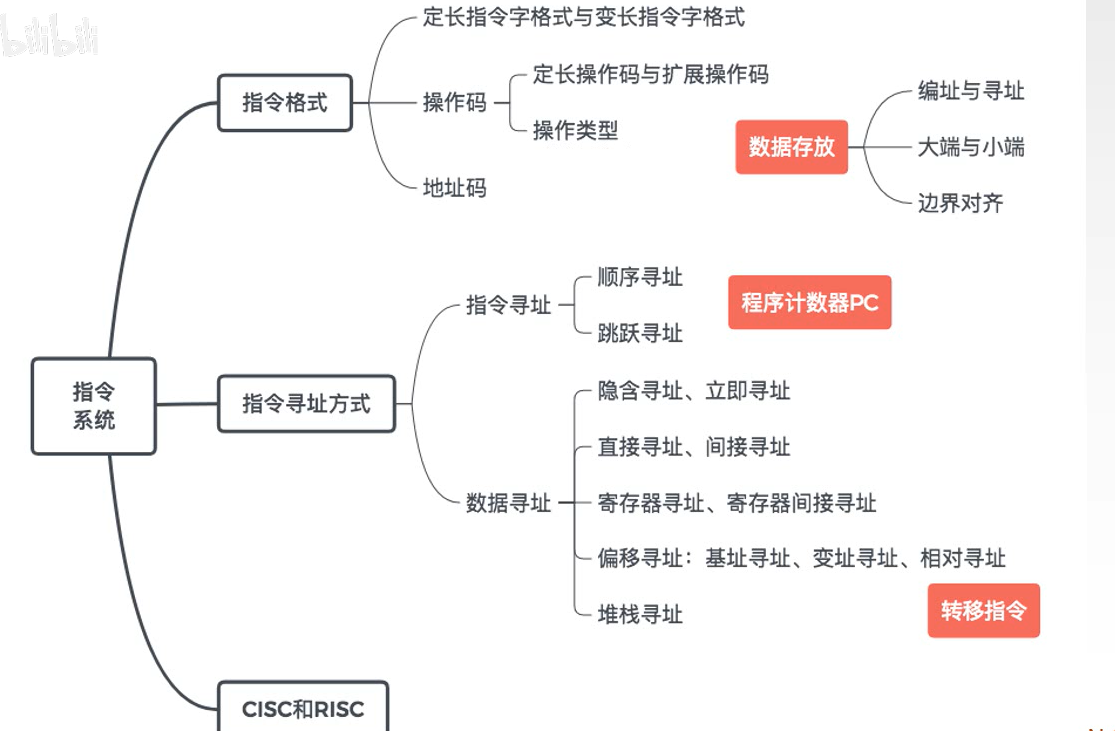

4.指令

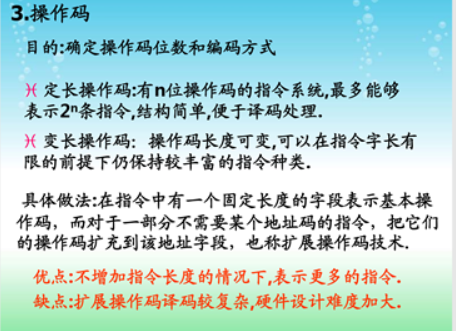

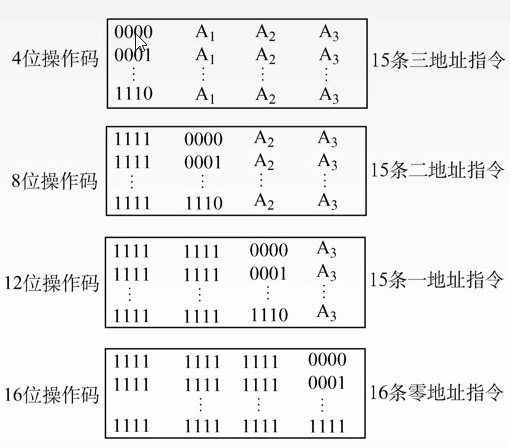

指令格式

指令的址方式

1.顺序寻址方式 2.跳跃寻址方式

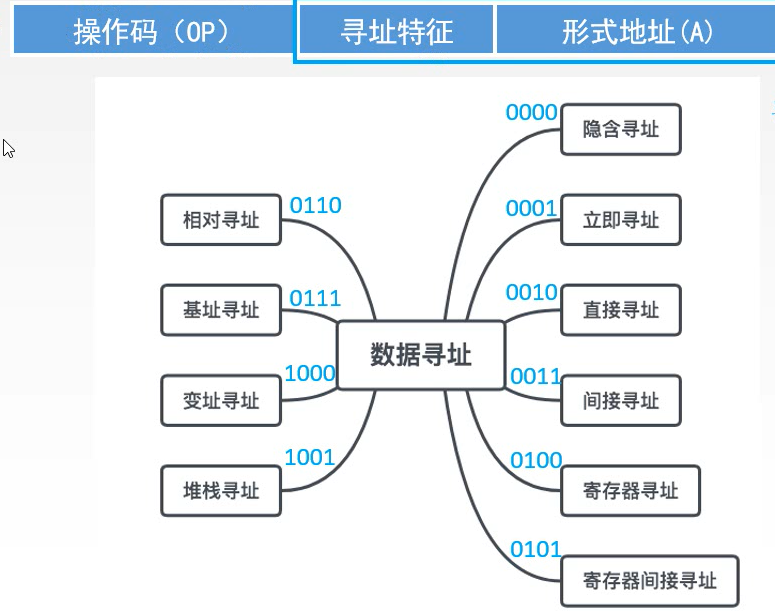

数据寻址方式

用寻址特征表明现在的寻址方式

立即寻址

寄存器寻址

直接寻址

寄存器间接寻址

基址寻址(BR)面向操作系统,内容操作系统确定,有利于多道程序数据块

变址寻址(IX)用于循环程序,数组的偏移

相对寻址(PC) (PC)+A 跳转指令

寄存器寻址:(SP)保存栈顶指针

间接寻址

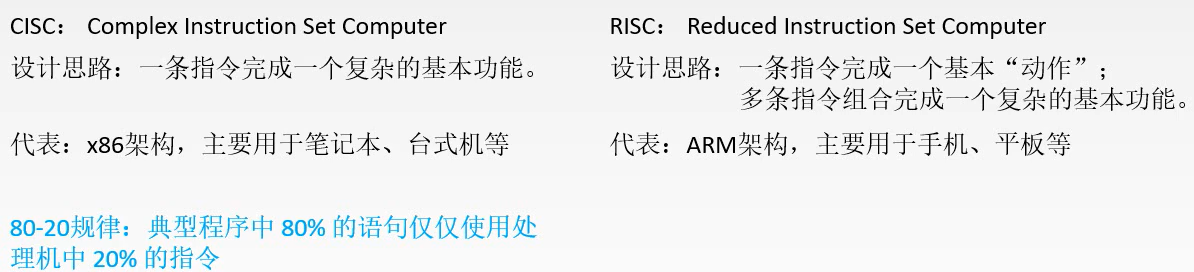

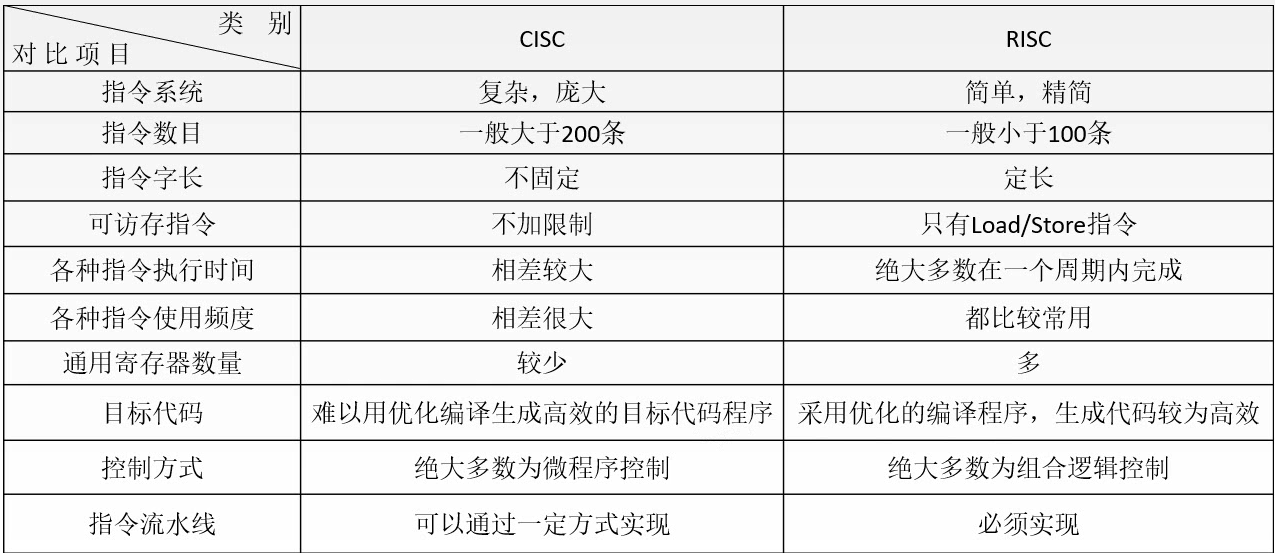

CISC、RISC

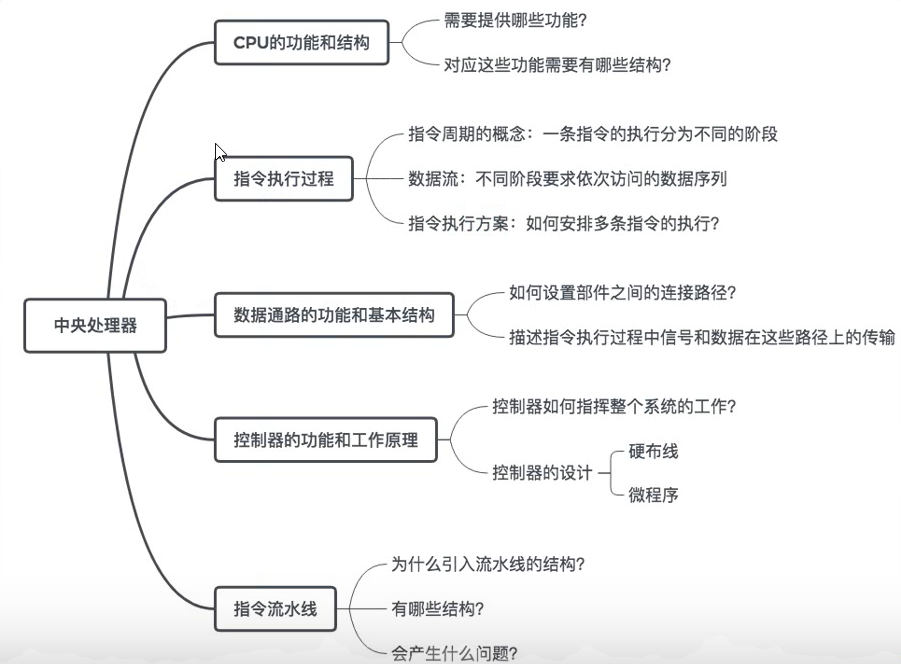

5.CPU

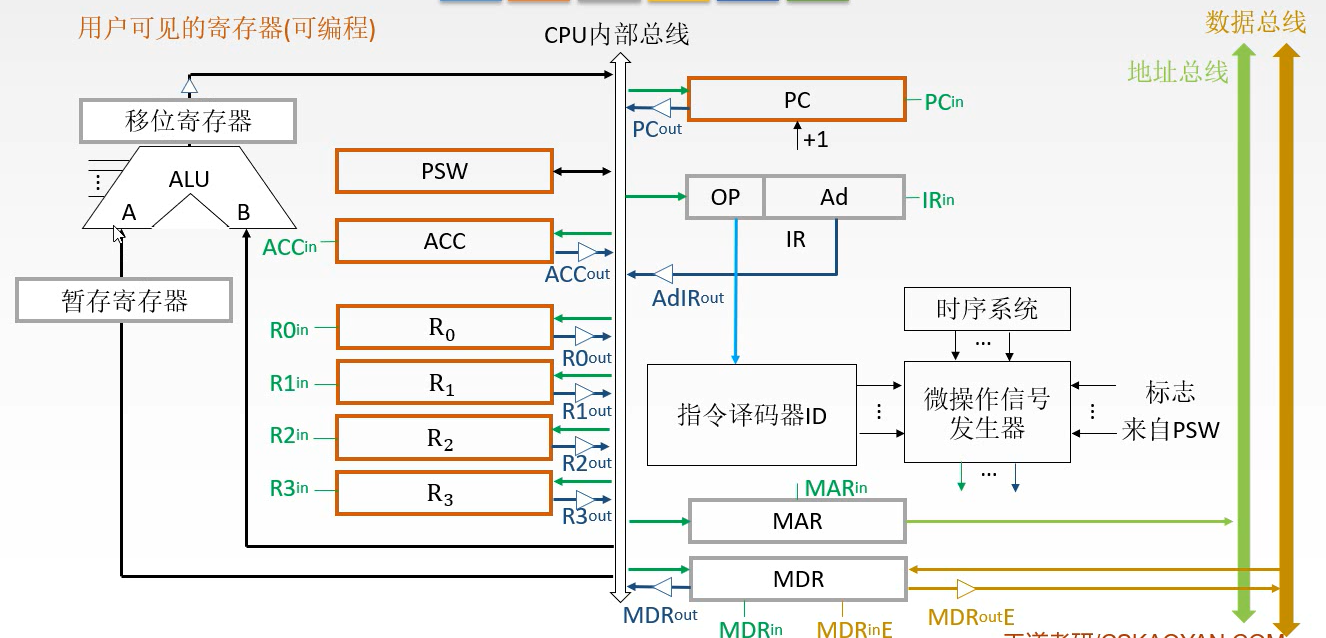

ALU+CU+寄存器+中断系统

CPU结构

cpu内部总线完成内部数据传输;MAR,MDR要和内外总线都要连接

还有一种结构为:寄存器之间通过专用线连接

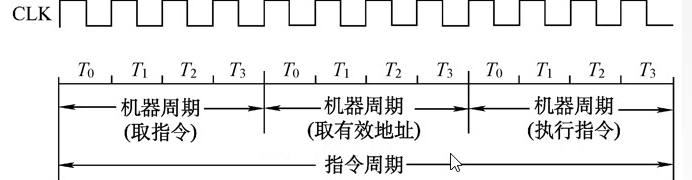

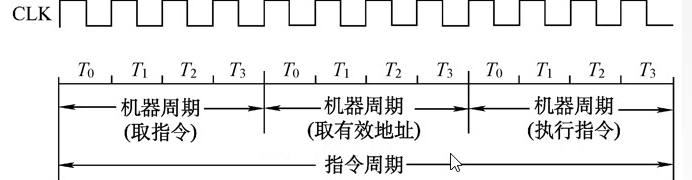

指令周期

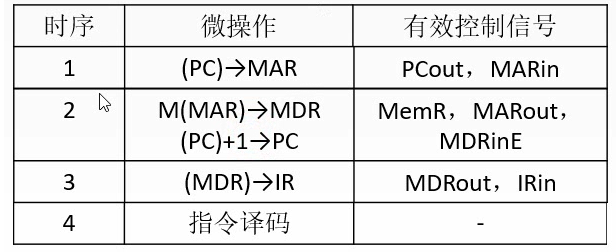

一个机器周期(CPU周期)是一次存取周期

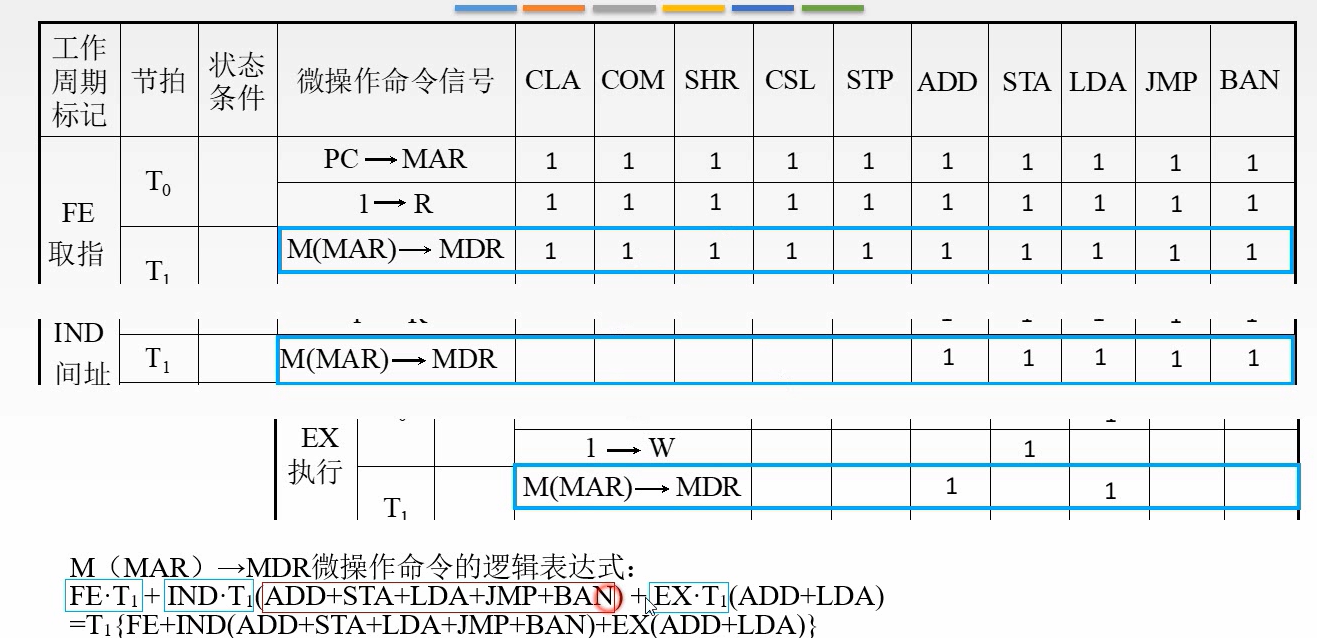

微操作

取指、取数

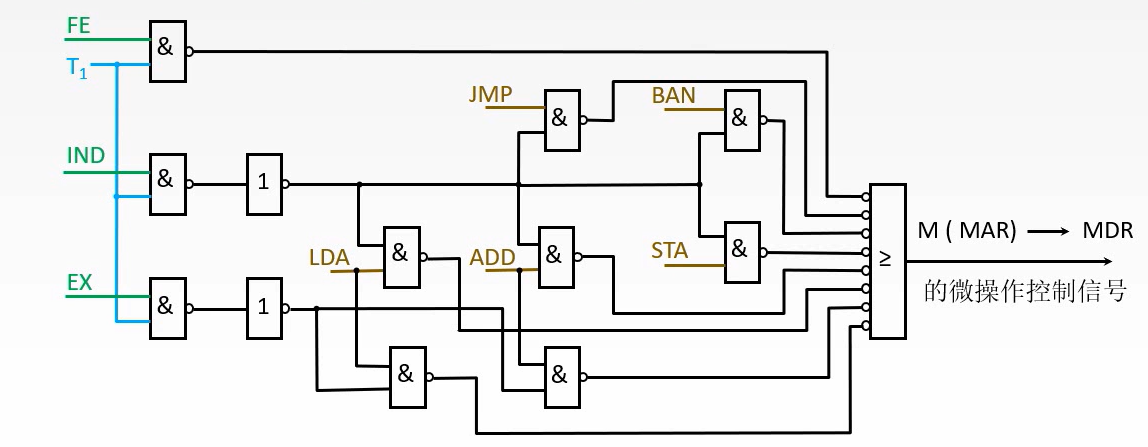

控制器

cpu控制方式:

同步控制方式、异步控制方式、联合控制方式

同步:

硬布线:RISC

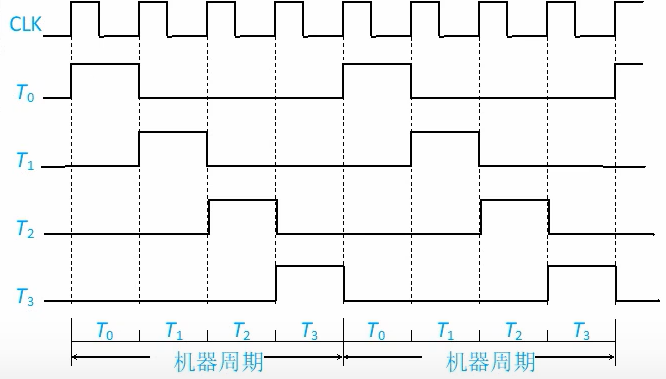

节拍发生器:将时钟转为节拍

安排微操作的时钟节拍

设计电路

微程序:CISC

将微指令保存到控制存储器CM中(CPU内部,ROM实现,一条条已经写好的),类似于指令的保存执行

水平型:可以同时执行。垂直型:类似机器指令

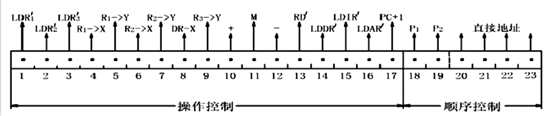

操作控制字段:标记一个个微操作,

直接表示法:为1就执行 需要很长 快

编码表示法

混合 组内互斥

组内互斥

顺序控制字段:下一条微指令是 跳转 还是 顺序

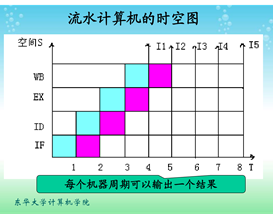

流水线

将这几个过程重叠起来,并行运行

问题:

时间不一样:全部统一为最长的时间

冲突:

硬件:

结构相关(资源冲突):硬件资源满足不了 同时需要访问内存

编程:

数据相关(数据冲突):一条指令依赖前一条指令的执行结果(数据)却无法得到 c=a+b; c++;

硬件直接暂停 添加空指令 数据旁路 编译优化

控制相关(控制冲突):流水线遇到分支(if) 指令或其他改变PC值的指令

(acm算法运行为非流水执行过程。)

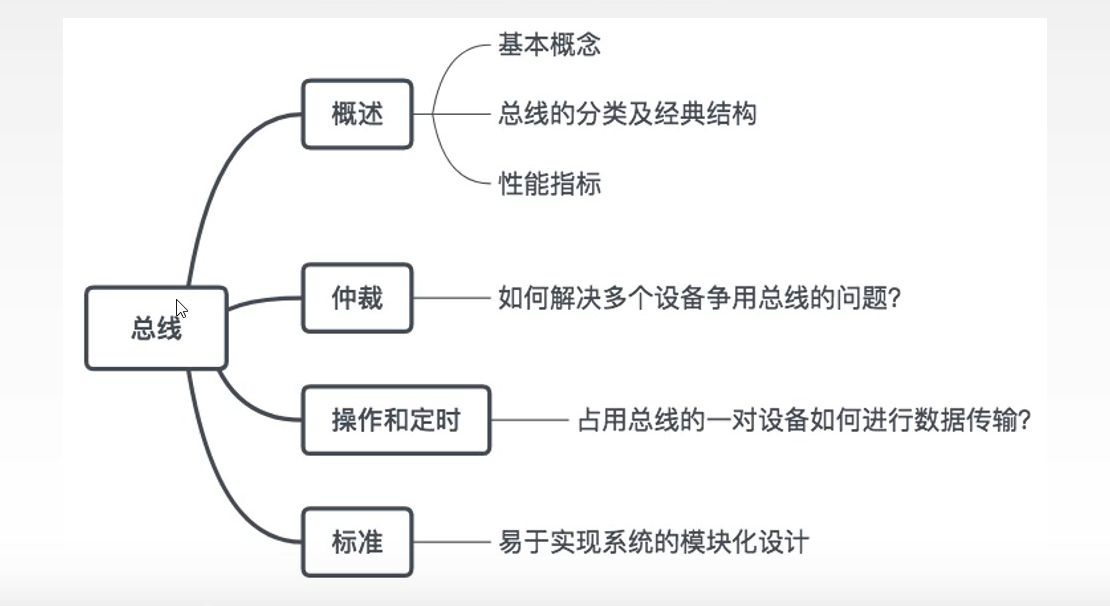

6.总线

分时 共享

机械特性、电器特性、功能特性、时间特性

分类

串行、并行(宽度高、频率低)

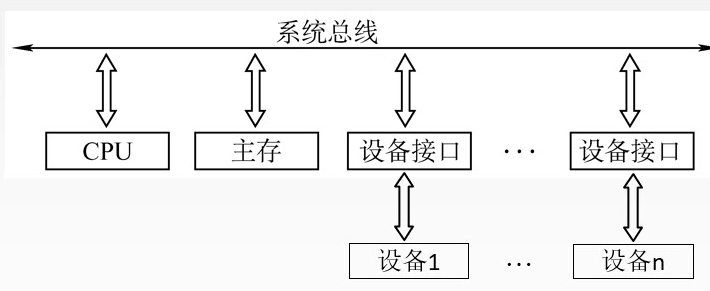

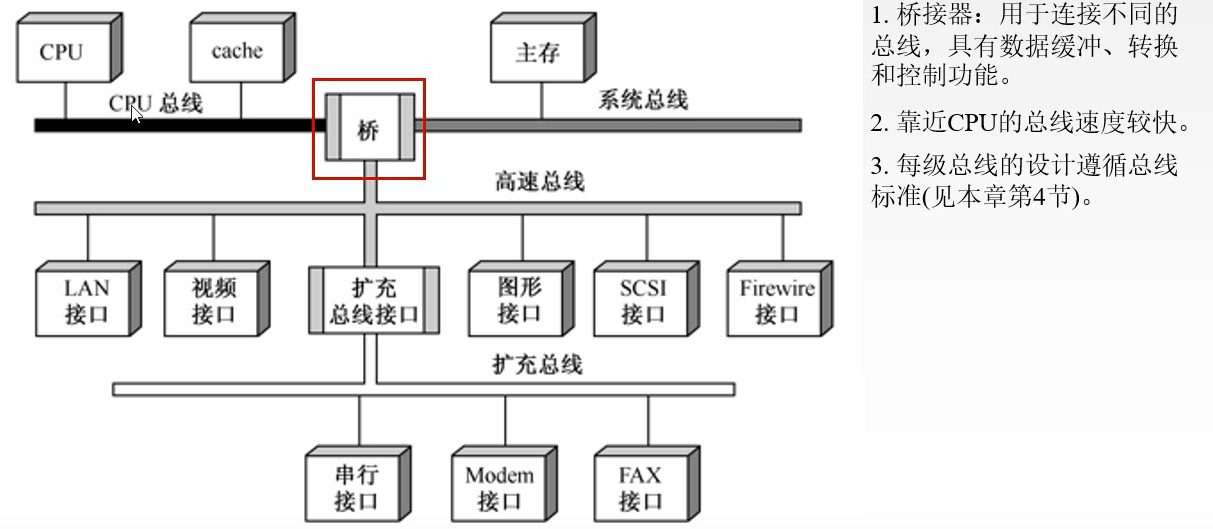

(内部总线、系统总线(数据、地址、控制)、I/O总线) 轮询

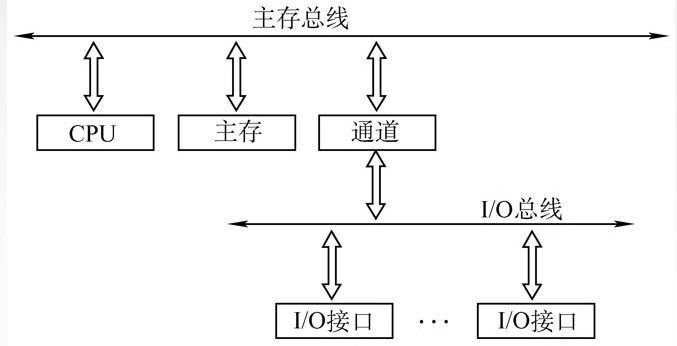

单总线 双总线(速度不同,进行分离)

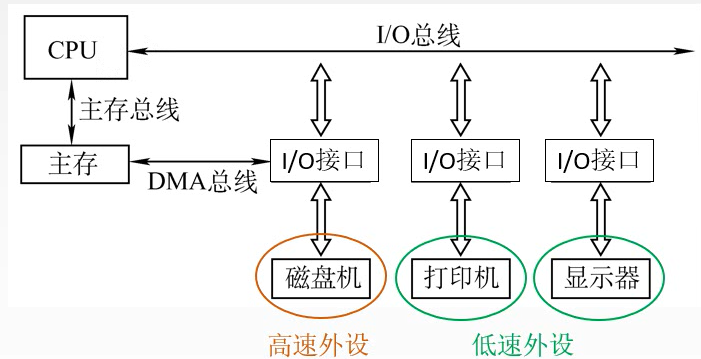

三总线(提高io速度) DMA控制器控制高速传输(不用CPU),别的中断(鼠标键盘)实现

4总线

地址总线(AB)—其宽度可表明地址空间范围 32位寻址范围2^32 4G

数据总线(DB)—其宽度可表明一次读写的二进制位数 32位4B

控制总线(CB)— 包括各种控制命令(如存储器读 写、I/O读写)、请求信号与仲裁信号、中断请求与应答 等。

复用AB和DB

性能指标

时钟周期T:机器的时钟周期 时钟频率:1/T

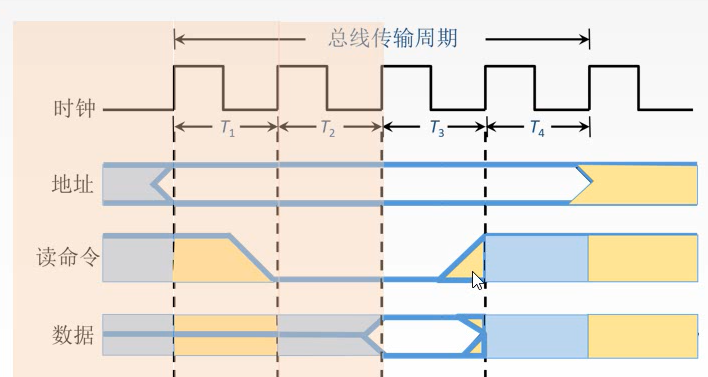

传输周期:N个时钟周期:申请、寻址、传输、结束 工作频率:1/N

总线宽度:DB宽度

总线带宽:每秒传输的B ,工作频率 * 总线带宽 / 8

总线仲裁

集中总裁

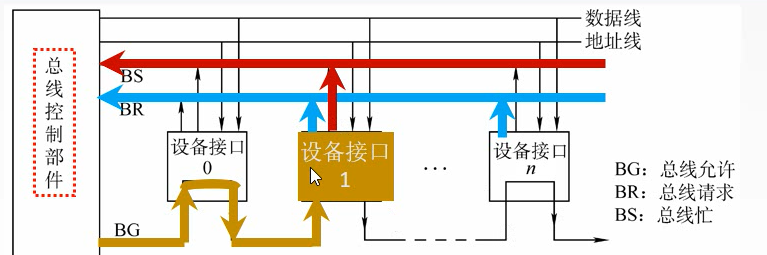

链式查询:BR BG BS , BG按顺序查询,距离近的优先级高

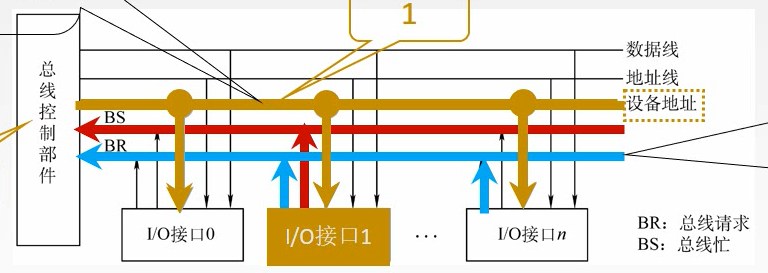

计算器定时查询:独立的BG线,计数器每次加1代表访问下一个IO , log n

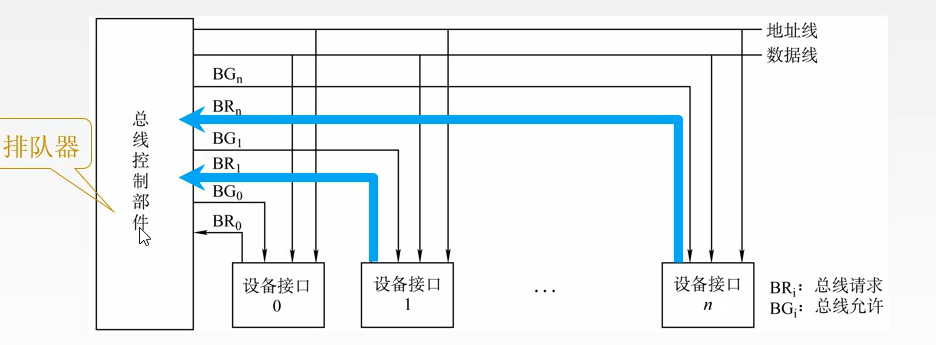

独立请求:需要排队、速度快。独立的BG线

分布式仲裁:

不需要中央仲裁器,每个潜在的主 方功能模块都有自己的仲裁号和仲裁器

将总裁号发到总裁总线上去比较

总线操作

申请分配(请求、仲裁)、寻址阶段、传输阶段、结束阶段

同步定时方式:根据时钟的上升沿控制节奏

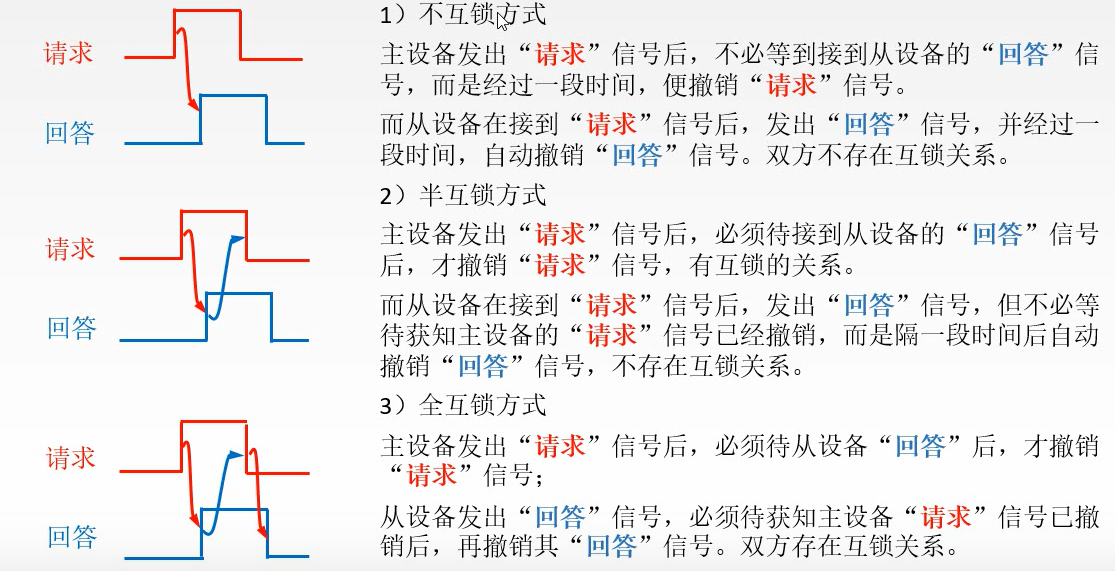

异步定时方式

半同步通信:加控制信号,当数据没传到位时等待

分离式通信:将准备数据时,总线控制权交出来

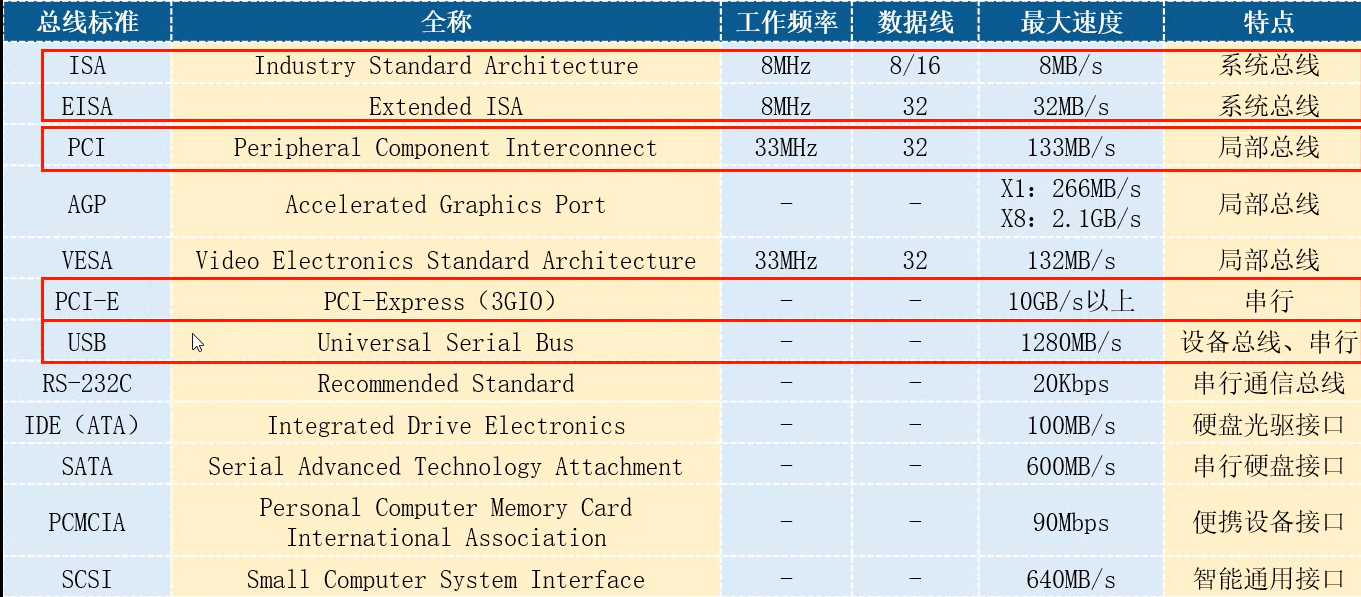

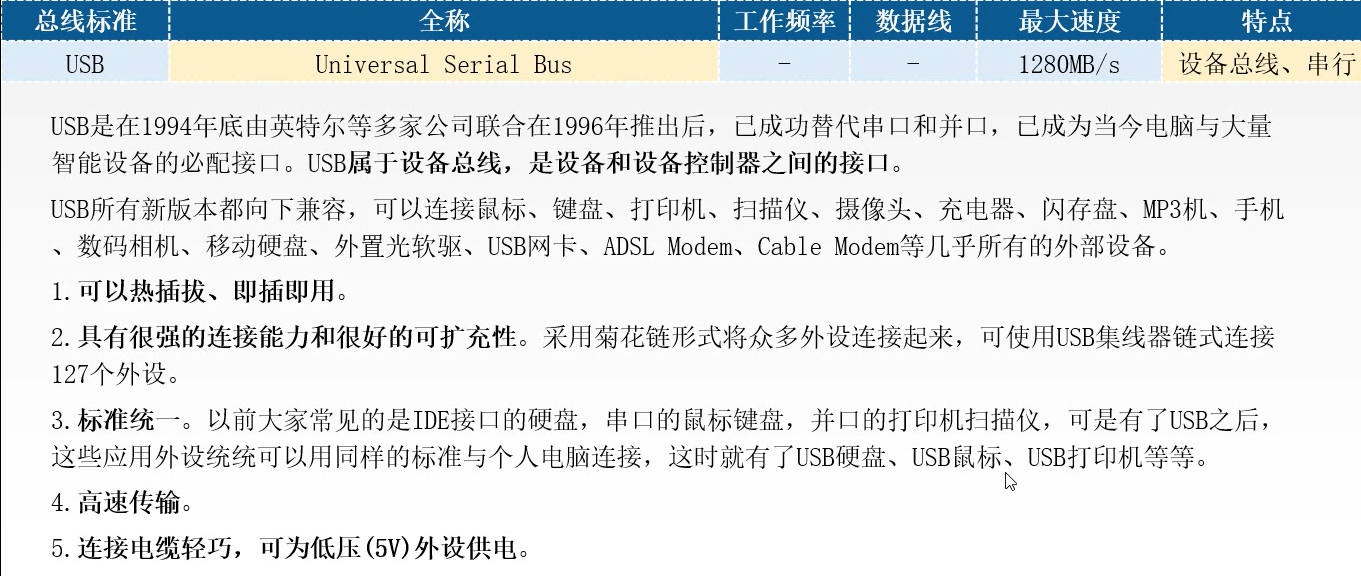

总线标准

7.IO

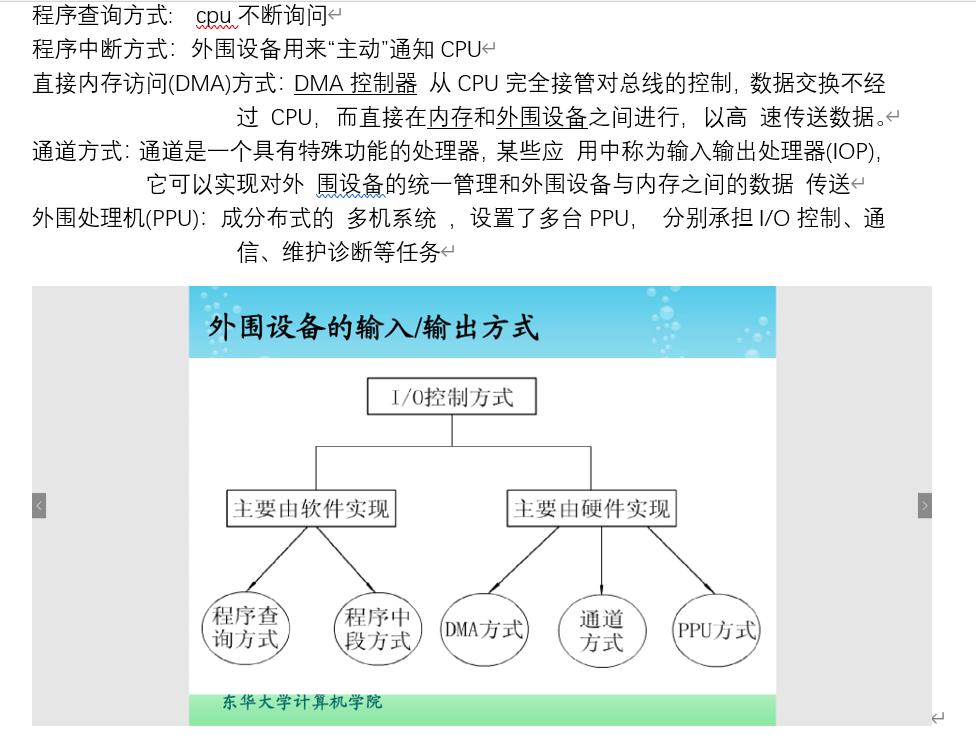

CPU管理外围设备有几种方式:

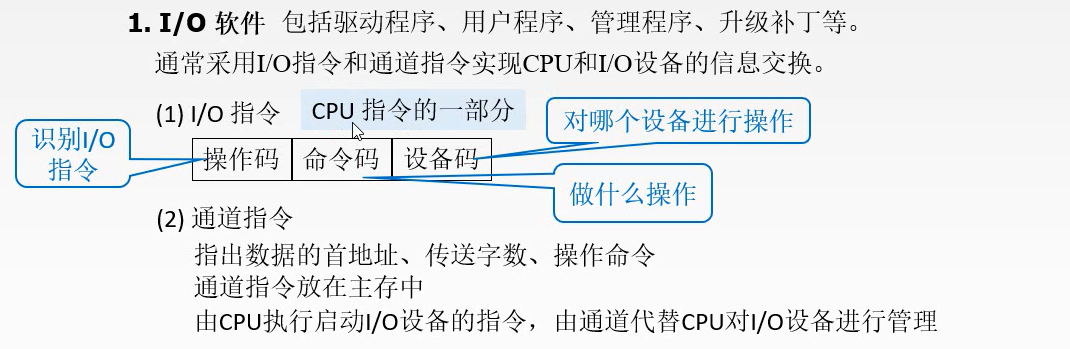

IO指令由CPU产生,用来控制IO;通道指令为通道产生,具体执行

输入输出设备

输入: 鼠标键盘 输出 :显示器打印机

外存

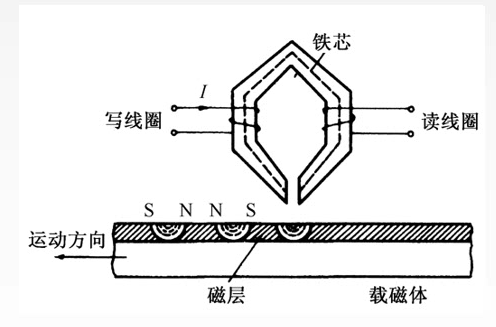

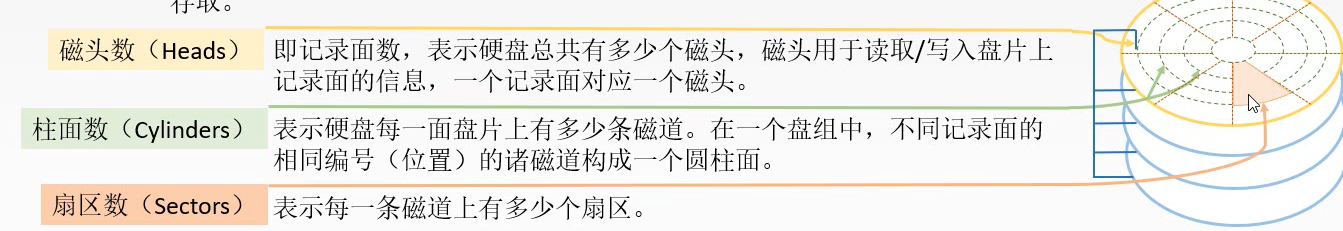

磁表面存储

串行读取

磁盘

按照扇区读取,寻道->旋转->传输时间。利用便宜可以实现加速或者冗余

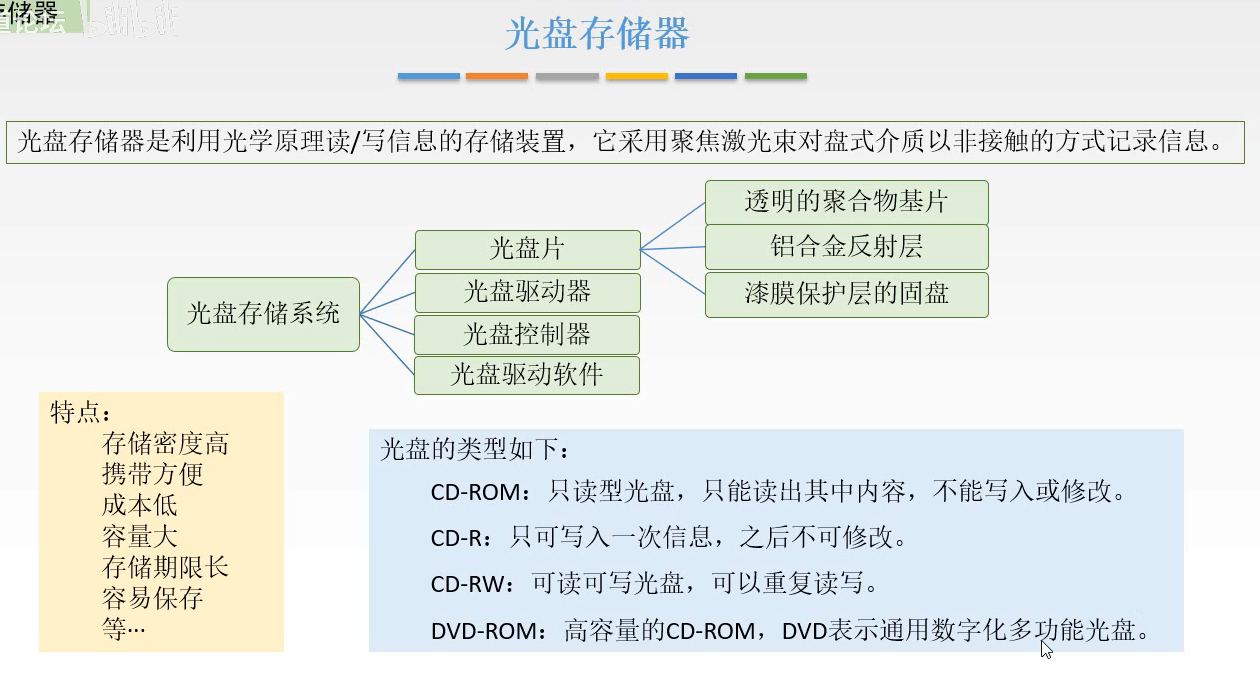

光盘

固态硬盘

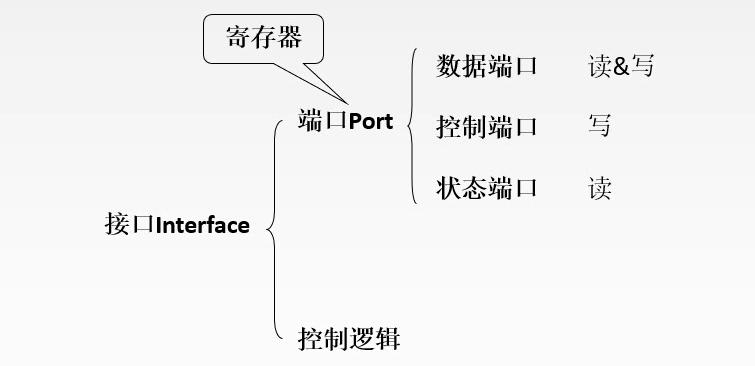

IO接口

控制、读取io其实就是访问响应寄存器

如何定位编址?统一编址、独立编址(主存的编址和IO的编址是否在一起)

查询方式

比如每秒查询鼠标30次,询问鼠标有没有数据。查到了还需要等待鼠标传输数据

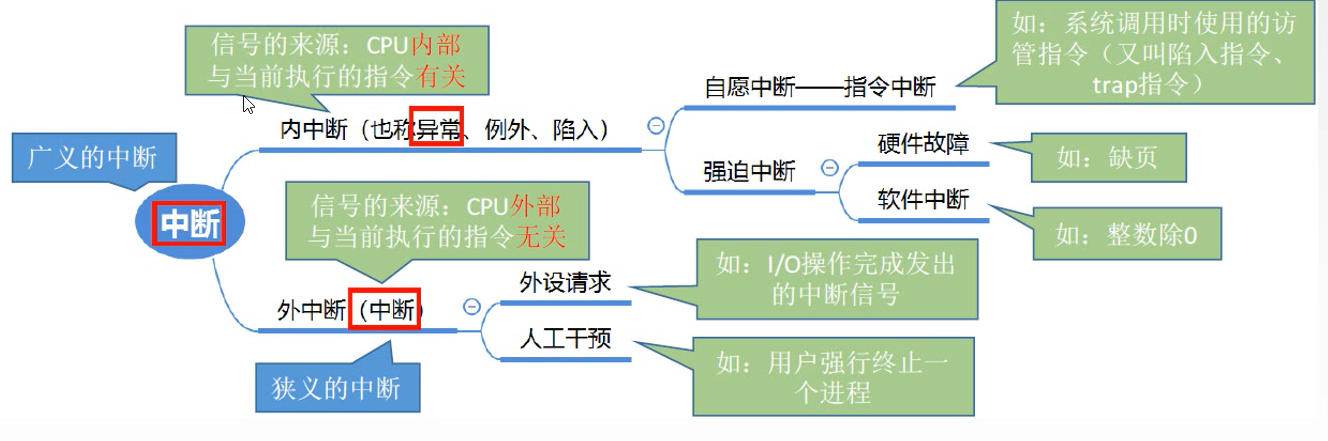

中断方式

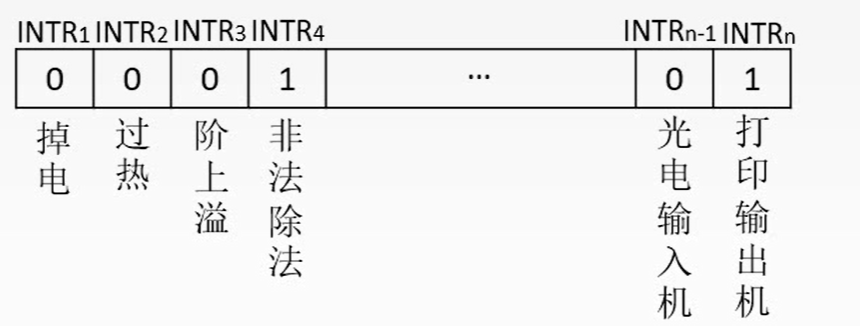

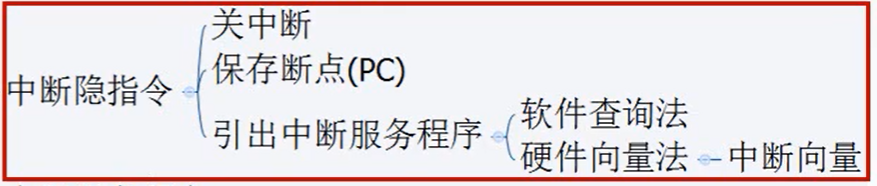

在指令完成后,查看中断源寄存器是否有1,有1就进入中断

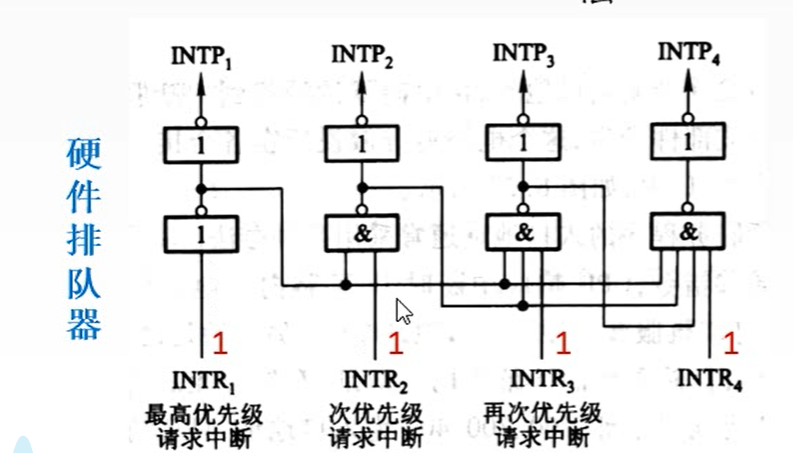

实现优先级

DMA

接收IO请求,向CPU发出占用总线的请求